## VIDEO PROCESSING APPLICATIONS OF HIGH SPEED CMOS IMAGE SENSORS

A DISSERTATION SUBMITTED TO THE DEPARTMENT OF ELECTRICAL ENGINEERING AND THE COMMITTEE ON GRADUATE STUDIES OF STANFORD UNIVERSITY IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

> Suk Hwan Lim March 2003

© Copyright by Suk Hwan Lim 2003 All Rights Reserved I certify that I have read this dissertation and that in my opinion it is fully adequate, in scope and quality, as a dissertation for the degree of Doctor of Philosophy.

Abbas El Gamal (Principal Adviser)

I certify that I have read this dissertation and that in my opinion it is fully adequate, in scope and quality, as a dissertation for the degree of Doctor of Philosophy.

Teresa Meng

I certify that I have read this dissertation and that in my opinion it is fully adequate, in scope and quality, as a dissertation for the degree of Doctor of Philosophy.

Brian Wandell

I certify that I have read this dissertation and that in my opinion it is fully adequate, in scope and quality, as a dissertation for the degree of Doctor of Philosophy.

John Apostolopoulos

Approved for the University Committee on Graduate Studies:

## Abstract

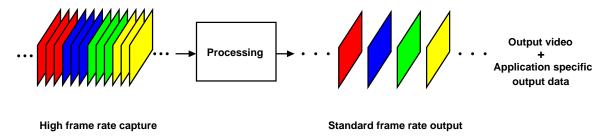

An important trend in the design of digital cameras is the integration of capture and processing onto a single CMOS chip. Although integrating the components of a digital camera system onto a single chip significantly reduces system size and power, it does not fully exploit the potential advantages of integration. We argue that a key advantage of integration is the ability to exploit the high speed imaging capability of CMOS image sensors to enable new applications and to improve the performance of existing still and video processing applications. The idea is to capture frames at much higher frame rates than the standard frame rate, process the high frame rate data on chip, and output the video sequence and the application specific data at standard frame rate.

In the first part of the dissertation we discuss two applications of this idea. The first is optical flow estimation, which is the basis for many video applications. We present a method for obtaining high accuracy optical flow estimates at a standard frame rate by capturing and processing a high frame rate version of the video, and compare its performance to methods that only use standard frame rate sequences. We then present a method that uses a video sequence and accurate optical flow estimates to correct sensor gain Fixed Pattern Noise (FPN). Simulation and experimental results demonstrate that significant reduction in gain FPN can be achieved using our method.

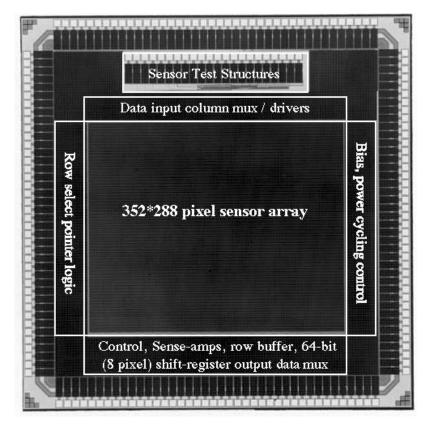

In the second part of the dissertation we discuss hardware implementation issues of high speed CMOS imaging systems. We designed, fabricated and tested a  $352 \times 288$ pixel CMOS Digital Pixel Sensor chip with per-pixel single-slope ADC and 8-bit dynamic memory in a standard digital  $0.18\mu$ m CMOS process. The chip performs "snap-shot" image acquisition at continuous rate of 10,000 frames/s or 1 Gpixels/s. We then discuss the projected limits of integrating memory and processing with a CMOS image sensor in  $0.18\mu$ m process and below. We show that the integration of an entire video camera system on a chip is not only feasible at  $0.18\mu$ m process, but in fact underutilizes the possible on-chip processing power. Further, we show that the projected available on-chip processing power and memory are sufficient to perform applications such as optical flow estimation.

## Acknowledgments

There is always too little to space when it comes to thanking all the people whom I spent considerable time together. Although some times were a little tough, I had wonderful time during my graduate studies at Stanford University and I am deeply indebted to many people.

First, I would like to thank my adviser Prof. Abbas El Gamal. It has been a great pleasure and honor to be one of his students. All this work would not have been possible without without his guidance and support. Especially, his broad knowledge in many areas of electrical engineering enabled me to obtain great academic advice from a wide range of fields. It also inspired me to conduct research in a broader way.

I would also like to thank professors who served on my orals and dissertation committee. I am grateful to Prof. Teresa Meng, my associate adviser, for her generous support and guidance especially during early part of my graduate studies. I want to thank Prof. Brian Wandell who led the Programmable Digital Camera (PDC) project together with Prof. El Gamal. It was almost like having another principal adviser. I am very grateful for that and it was such a great pleasure to work with him. I also would like to thank Dr. John Apostolopoulos. Part of my optical flow estimation research conducted done while I was taking his video processing class. Not only did he give me great advice for my research, but has been and is a great mentor for me. I truly appreciate it.

Also, I want to thank Prof. Tomasi, Dr. Fleet, Prof. Heeger and Prof. Godfrey for valuable discussions and comments. I would also like to thank my former and current group members. Dr. David Yang, Dr. Boyd Fowler, Dr. Hui Tian, Dr. Xinqiao Liu, Ting Chen, Khaled Salama, Helmy Eltoukhy, Sam Kavusi, Ali Ozer, Sina Zahedi and Hossein Kakavand. I am reluctant to call them as group members since they are more like friends. They made my life at Stanford pleasing and enjoyable. I would also like to thank Charlotte Coe, Kelly Yilmaz and Denise Cuevas for their assistance.

I also like to thank the sponsors of PDC project for funding major part of my graduate studies. I would like to thank DARPA for partially supporting me during my graduate studies in Stanford.

I wish to thank all my friends at Stanford with whom I had lots of fun with. To name a few, Eun Sun Park, Haktae Lee, SoYoung Kim, Gwang Hyun Gho, Paul Wang Lee, JiHi Jung, Jaewook Kim, Nahmsuk Oh, Eui-Young Chung, Sunghee Yun, Mario Mendoza, Mai-Sie Chan, Xin Tong, Wonjong Rhee and Sangeun Han. They all have been great in helping me out and I was able to have lots of fun with them. I would also like to thank all my friends both in U.S. and Korea for their company and support, especially my Seoul Science High School alumni friends and HwaHyunHoi friends.

Last, but definitely not the least, I would like to thank my family. I would never be where I am if it were not for their unconditional love and support. I dedicate my thesis to my family.

# Contents

| A            | bstra | ict    |                                                    | iv |

|--------------|-------|--------|----------------------------------------------------|----|

| $\mathbf{A}$ | ckno  | wledgr | nents                                              | vi |

| 1            | Intr  | oducti | ion                                                | 1  |

|              | 1.1   | Digita | l cameras and image sensors                        | 1  |

|              | 1.2   | High f | rame rate capture – standard frame rate output     | 6  |

|              | 1.3   | Thesis | organization                                       | 8  |

| <b>2</b>     | Opt   | ical F | low Estimation                                     | 10 |

|              | 2.1   | Introd | luction                                            | 10 |

|              | 2.2   | Optica | al flow estimation using high frame rate sequences | 12 |

|              |       | 2.2.1  | Proposed method                                    | 12 |

|              |       | 2.2.2  | Simulation and results                             | 17 |

|              | 2.3   | Effect | of motion aliasing on optical flow estimation      | 20 |

|              |       | 2.3.1  | Review of spatio-temporal sampling theory          | 21 |

|              |       | 2.3.2  | Simulation and results                             | 26 |

|              | 2.4   | Exten  | sion to handle brightness variation                | 31 |

|              |       | 2.4.1  | Review of models for brightness variation          | 31 |

|              |       | 2.4.2  | Using Haussecker method with high frame rate       | 33 |

|              | 2.5   | Summ   | ary                                                | 35 |

| 3            | Gai   | n Fixe | d Pattern Noise Correction                         | 37 |

|              | 3.1   | Introd | luction                                            | 37 |

|          | 3.2   | Image and fixed pattern noise model          | 39 |

|----------|-------|----------------------------------------------|----|

|          | 3.3   | Description of the algorithm                 | 42 |

|          |       | 3.3.1 Integer displacements                  | 42 |

|          |       | 3.3.2 Non-integer displacements              | 45 |

|          | 3.4   | Results                                      | 48 |

|          | 3.5   | Complexity                                   | 53 |

|          | 3.6   | Summary                                      | 55 |

| 4        | Har   | dware and Implementation Issues              | 56 |

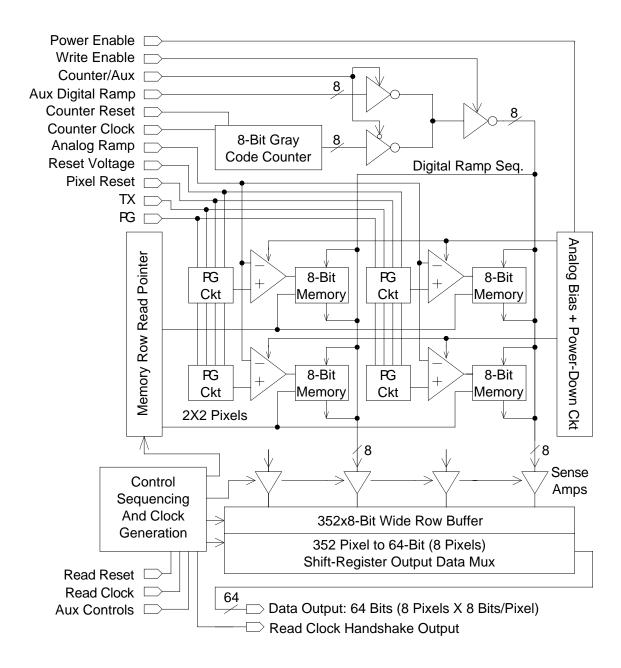

|          | 4.1   | A 10,000 frames/s Digital Pixel Sensor (DPS) | 56 |

|          |       | 4.1.1 DPS chip overview                      | 57 |

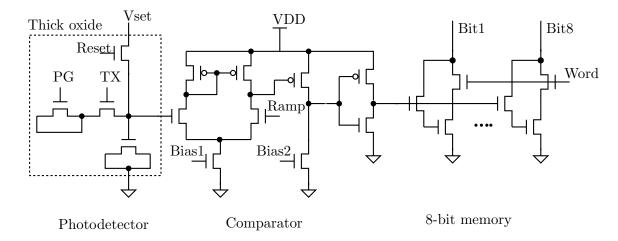

|          |       | 4.1.2 Pixel design                           | 61 |

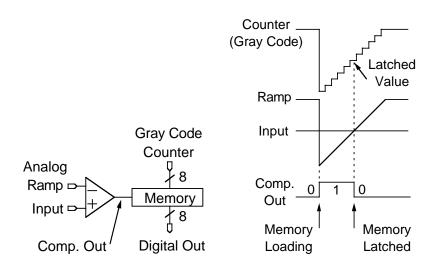

|          |       | 4.1.3 Sensor operation                       | 64 |

|          |       | 4.1.4 Testing and characterization           | 66 |

|          |       | 4.1.5 Summary                                | 69 |

|          | 4.2   | Memory and processing integration limits     | 69 |

| <b>5</b> | Sun   | nmary and Future Work                        | 75 |

|          | 5.1   | Summary                                      | 75 |

|          | 5.2   | Recommendation for future work               | 78 |

| Bi       | bliog | graphy                                       | 80 |

# List of Tables

| 2.1 | Average angular error and magnitude error using Lucas-Kanade method            |    |  |

|-----|--------------------------------------------------------------------------------|----|--|

|     | with standard frame rate sequences versus the proposed method using            |    |  |

|     | high frame rate sequences                                                      | 19 |  |

| 2.2 | Average angular and magnitude error using Lucas-Kanade, Anandan's              |    |  |

|     | and proposed method.                                                           | 20 |  |

| 2.3 | Average angular error and magnitude error using Haussecker's method            |    |  |

|     | with $OV = 1$ sequences versus proposed extended method with $OV =$            |    |  |

|     | 4 sequences                                                                    | 35 |  |

| 4.1 | Chip characteristics.                                                          | 59 |  |

| 4.2 | DPS chip characterization summary. All numbers, except for power               |    |  |

|     | consumption are at 1000 frames/s. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 67 |  |

| 4.3 | Processing and memory required to implement digital video camera               |    |  |

|     | system                                                                         | 72 |  |

|     |                                                                                |    |  |

# List of Figures

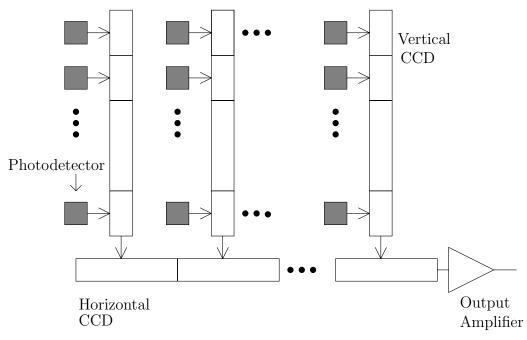

| 1.1 | Block diagram of a typical CCD image sensors.                        | 2  |

|-----|----------------------------------------------------------------------|----|

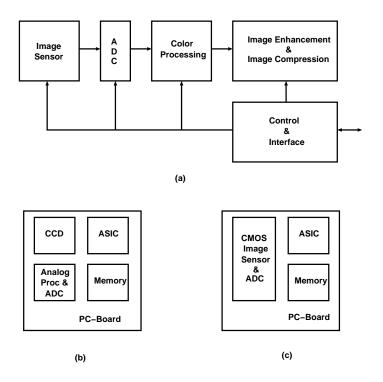

| 1.2 | Digital Camera System: (a) functional block diagram, (b) implemen-   |    |

|     | tation using CCD, and (c) implementation using CMOS image sensor.    | 3  |

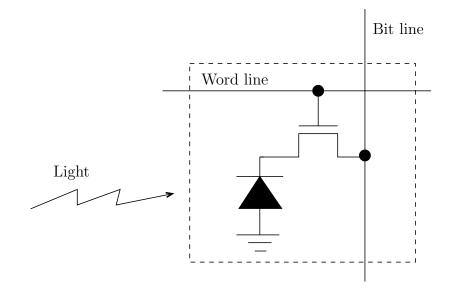

| 1.3 | Passive pixel sensor (PPS)                                           | 4  |

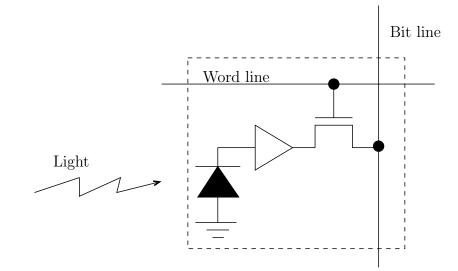

| 1.4 | Active Pixel Sensor (APS)                                            | 5  |

| 1.5 | Digital Pixel Sensor (DPS)                                           | 5  |

| 1.6 | High frame rate capture – standard frame rate output                 | 7  |

| 2.1 | The block diagram of the proposed method $(OV = 3)$                  | 13 |

| 2.2 | Block diagram of Lucas-Kanade method. Note that the last three       |    |

|     | blocks are performed for each pixel of each frame                    | 13 |

| 2.3 | The accumulation of error vectors when accumulating optical flow     |    |

|     | without using refinement.                                            | 15 |

| 2.4 | Accumulate and refine stage                                          | 16 |

| 2.5 | (a) One frame of a test sequence and (b) its known optical flow      | 19 |

| 2.6 | Spatio-temporal spectrum of a temporally sampled video               | 22 |

| 2.7 | Minimum $OV$ to avoid motion aliasing, as a function of horizontal   |    |

|     | velocity $v_x$ and horizontal spatial bandwidth $B_x$                | 23 |

| 2.8 | Wagon wheel rotating counter-clockwise illustrating motion aliasing  |    |

|     | from insufficient temporal sampling: the local image regions (gray   |    |

|     | boxes) appear to move clockwise.                                     | 24 |

| 2.9 | Spatio-temporal diagrams of, (A) the shaded region in Figure 2.8 and |    |

|     | (B) its baseband signal.                                             | 25 |

| 2.10 | Minimum $OV$ as a function of horizontal velocity $v_x$ and horizontal             |

|------|------------------------------------------------------------------------------------|

|      | spatial frequency $f_x$                                                            |

| 2.11 | Difference between the empirical minimum $OV$ and $OV$ corresponding               |

|      | to the Nyquist rate                                                                |

| 2.12 | Difference between the empirical minimum $OV$ and $OV$ corresponding               |

|      | to the 1.55 times the Nyquist rate.                                                |

| 2.13 | Average angular error versus oversampling factor $(OV)$                            |

| 2.14 | Average angular error versus energy in the image that leads to motion              |

|      | aliasing.                                                                          |

| 3.1  | An image and its histogram of uniform illumination illustrating FPN                |

| 3.2  | Sequence of frames with brightness constancy                                       |

| 3.3  | 1-D case simple example when the displacements are integers                        |

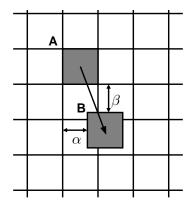

| 3.4  | Non-integer $d_x$ and $d_y$ displacements                                          |

| 3.5  | 1-D case simple example when the displacements are non-integers                    |

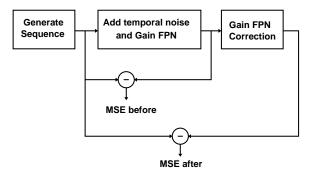

| 3.6  | Simulation setup.                                                                  |

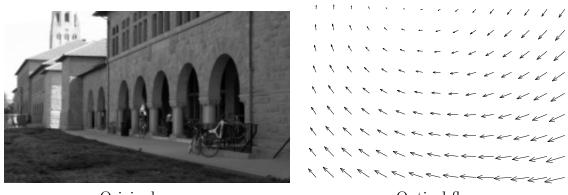

| 3.7  | Original scene and its optical flow.                                               |

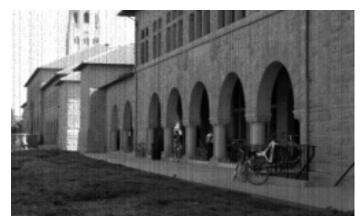

| 3.8  | Images before and after correction with 5% of pixel gain variation                 |

| 3.9  | Images before and after correction with $3\%$ of pixel and $4\%$ of column         |

|      | gain variation.                                                                    |

| 3.10 | Images before and after correction for real sequence                               |

| 3.11 | Zoomed in images before and after correction for real sequence                     |

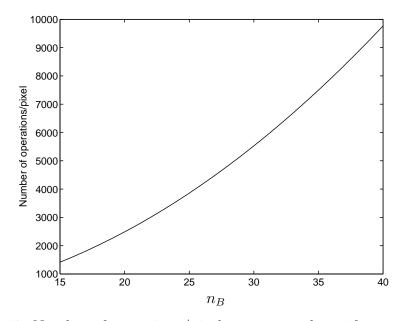

| 3.12 | Number of operations/pixel versus $n_B$ when 5 frames are used                     |

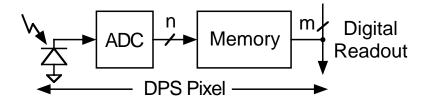

| 4.1  | Simple DPS pixel block diagram.                                                    |

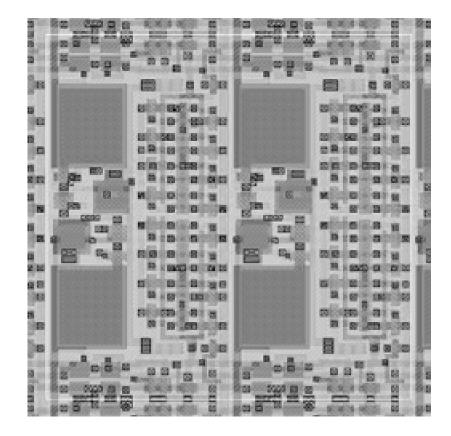

| 4.2  | DPS Chip photomicrograph. The chip size is $5 \times 5$ mm                         |

| 4.3  | DPS block diagram                                                                  |

| 4.4  | Pixel schematic.                                                                   |

| 4.5  | DPS pixel layout (2 × 2 pixel block shown). Pixel size is $9.4 \times 9.4 \mu m$ . |

| 4.6  | Single-slope ADC operation                                                         |

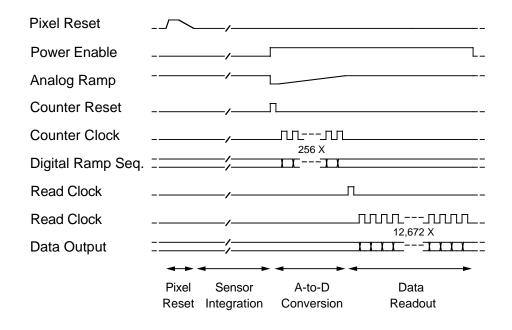

| 4.7  | Simplified DPS timing diagram                                                      |

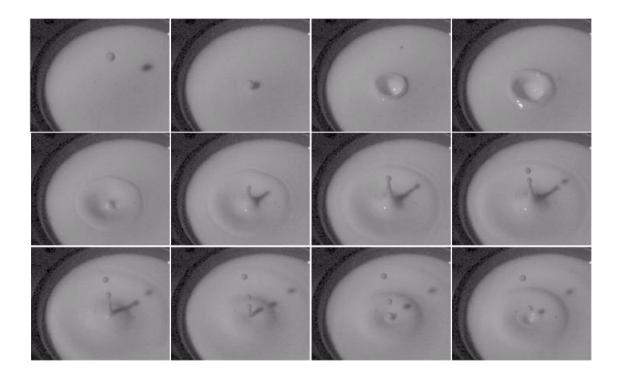

| 4.8  | A 700 frames/s video sequence (frames $100, 110, \ldots, 210$ are shown).          |

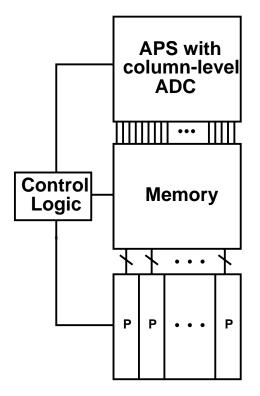

| 4.9  | Single chip imaging system architecture.                                             | 70 |

|------|--------------------------------------------------------------------------------------|----|

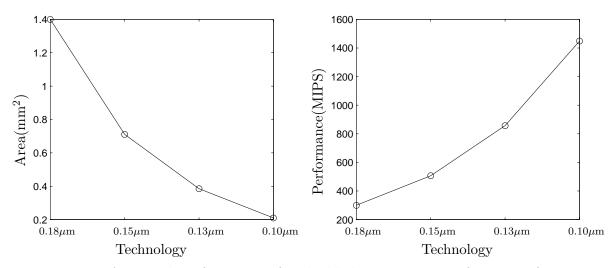

| 4.10 | Area and performance of embedded processor as a function of process                  |    |

|      | generation                                                                           | 71 |

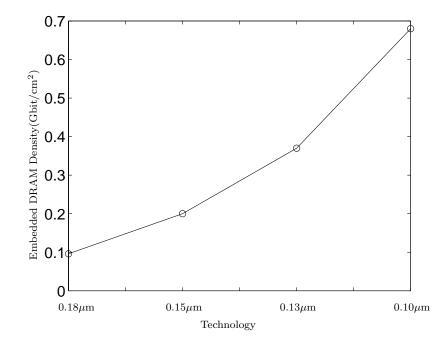

| 4.11 | Embedded DRAM density as a function of process generation                            | 72 |

| 4.12 | Maximum number of operations/pixel·frame vs. maximum number of                       |    |

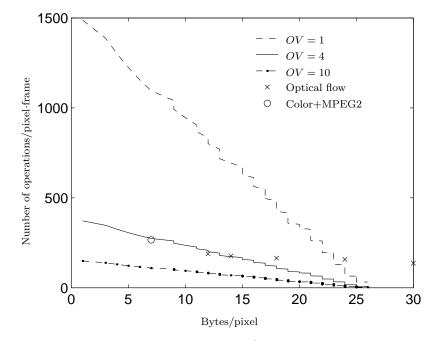

|      | bytes/pixel in 0.18 $\mu$ m CMOS process                                             | 73 |

| 4.13 | Maximum number of operations/pixel·frame vs. maximum number of                       |    |

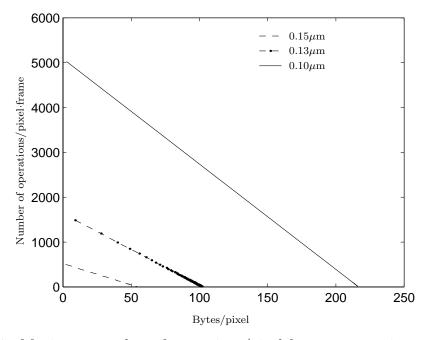

|      | bytes/pixel in $0.15\mu m$ , $0.13\mu m$ and $0.10\mu m$ technologies at $OV = 10$ . | 74 |

# Chapter 1

### Introduction

#### **1.1** Digital cameras and image sensors

Digital still and video cameras are rapidly becoming ubiquitous, due to reduced costs and increasing demands of multimedia applications. Digital still cameras are especially becoming very popular and are rapidly replacing analog and film cameras. Although replacing film cameras is one of many approaches one can take for digital imaging, it does not fully exploit the capabilities of digital imaging. Especially with the emergence of CMOS image sensors, digital still and video cameras enable many new imaging applications such as machine vision, biometrics and image-based rendering. Moreover, with miniaturization and cost reduction, image sensors can be embedded in virtually every multimedia system such as PC-based web cameras, cell phones, PDAs, games and toys.

Every digital imaging system employs an image sensor which converts light signals into electrical signals. The image sensor plays a pivotal role in the final image quality. Most of digital cameras today use the charge-coupled devices (CCDs) to implement the image sensors [1]-[8]. In the CCD image sensors, incident photons are converted to charge which are then accumulated by the photodetectors during exposure time. During the following readout, the accumulated charge in the array is sequentially transferred into the vertical and horizontal CCDs and finally shifted out to chip level output amplifier where it is converted to voltage signal as is shown in Figure 1.1. CCDs generally consume lots of power because of high capacitance and high switching frequency. Since CCD image sensor is fabricated using specialized process with optimized photodetectors, it has very low noise and good uniformity but cannot be integrated with memory and processing which are typically implemented in CMOS technology. Thus, a typical digital camera system today (see Figure 1.2) employs a CCD image sensor and several other chips for analog signal generation, A/D conversion, digital image processing and compression, control, interface, and storage.

Figure 1.1: Block diagram of a typical CCD image sensors.

In contrast, recently developed CMOS image sensors are fabricated using standard CMOS process with no or minor modification [9]-[11]. Similar to CCDs, incident photons are converted to charge which are then accumulated by the photodetectors during exposure time. Unlike CCDs, however, charge (or voltage) in the pixel array are read out using the row decoders and column amplifiers and multiplexers. This readout scheme is similar to a memory structure. Currently, there are three pixel architectures for CMOS image sensors: Passive Pixel Sensor (PPS), Active Pixel

Figure 1.2: Digital Camera System: (a) functional block diagram, (b) implementation using CCD, and (c) implementation using CMOS image sensor.

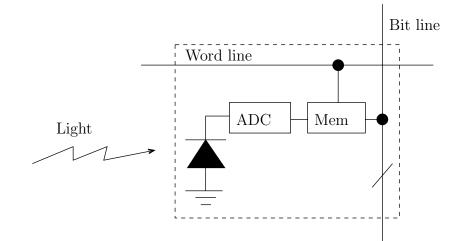

Sensor (APS) and Digital Pixel Sensor (DPS). PPS [12]-[18] has only one transistor per pixel, as shown in Figure 1.3. The charge in each pixel is read out via a column charge amplifier located outside of the pixel array. Although PPS has small pixel size and large fill factor, it suffers from slow readout speed and low SNR. APS [19]-[33] tries to solve these problems by having a buffer in each pixel, which is normally implemented with three or four transistors (see Figure 1.4). In comparison to PPS, APS has larger pixel size and lower fill factor, but its readout is faster and has higher SNR. In DPS, each pixel has an ADC and all ADCs operate in parallel as shown in Figure 1.5. With an ADC per pixel, massively parallel A/D conversion and high speed digital readout become practical, eliminating analog A/D conversion and readout bottlenecks. The main drawback of DPS is its large pixel size due to the increased number of transistors per pixel, which is less problematic as CMOS technology scales down to  $0.18\mu$ m and below.

Figure 1.3: Passive pixel sensor (PPS)

Regardless of the architecture, current CMOS image sensors typically have lower image quality and higher noise level than CCD image sensor, mainly because the fabrication process cannot be optimized for image sensing. Moreover, it has higher fixed pattern noise since image data are read out through different chains of buffers

Figure 1.4: Active Pixel Sensor (APS)

Figure 1.5: Digital Pixel Sensor (DPS)

and amplifiers. CMOS image sensors, however, have other unique advantages over CCDs. First, CMOS image sensors consume much less power than CCD image sensor due to lower voltage swing, switching frequency and capacitance. Second, integrating image sensing with A/D conversion, memory and processing on a single chip is possible for CMOS image sensor. Several researchers [34, 35, 36, 37] have exploited these advantages and have demonstrated low power consumption and reduction in chip count for a digital camera system by integrating the analog signal generation, A/D conversion, and some of the control and image processing with the sensor on the same chip. Loinaz *et al.* [35] describe a PC-based single chip digital color camera, which performs image capturing using a photogate APS, automatic gain control, an 8-bit full flash ADC, and all the computationally intensive pixel-rate tasks such as color interpolation, color correction, and image statistics computation. Smith *et al.* [36] describe a single chip CMOS NTSC video camera that integrates an APS, a half-flash sub-ranging ADC, and all the processing necessary to produce color NTSC video with only an external power supply and a crystal oscillator.

# 1.2 High frame rate capture – standard frame rate output

Commercially available PC camera chips now routinely integrate A/D conversion, gamma correction, exposure and gain control, color correction and white balance with a CMOS CIF and VGA size image sensor. As CMOS image sensors scale to  $0.18\mu$ m processes and below, integration of the rest of the camera system becomes feasible resulting in true "camera-on-chip". Although integrating the camera system shown in Figure 1.2 onto a single chip can significantly reduce system size and power, it does not fully exploit the potential advantages of integration. In this dissertation we argue that a key advantage of integration is the ability to exploit the high speed imaging capability of CMOS image sensors. Several recent papers have demonstrated the high speed imaging capability of CMOS image sensors [38, 39, 40, 41]. Krymski *et al.* [38] describe a  $1024 \times 1024$  Active Pixel Sensor (APS) with column level ADC achieving

frame rate of 500 frames/s. Stevanovic *et al.* [39] describe  $256 \times 256$  APS with 64 analog outputs achieving frame rate of 1000 frames/s. Kleinfelder *et al.* [40] describe a  $352 \times 288$  Digital Pixel Sensor(DPS) with per pixel bit parallel ADC achieving 10,000 frames/s or 1 Giga-pixels/s.

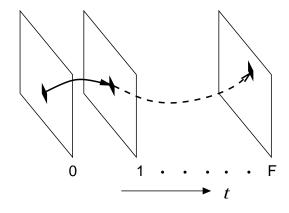

The high speed imaging capability of CMOS image sensors can benefit conventional camera systems by enabling more efficient implementations of several applications such as motion estimation [42], video stabilization, and video compression, and of new applications such as multiple capture for enhancing dynamic range [43, 44, 45] and motion blur-free capture [46]. Digital still and video cameras, however, operate at low frame rates and it would be too costly, if not infeasible, to operate them at high frame rates due to the high output data rate requirements of the sensor, the memory, and the processing chips. Integrating the memory and processing with the sensor on the same chip solves the high output data rate problem and provides an economical way to exploit the high speed capability of a CMOS image sensor. The basic idea, which will be explored in this dissertation (see Figure 1.6 and Handoko et al. [42, 47]), is to (i) operate the sensor at a much higher frame rate than the standard frame rate, (ii) exploit the high on-chip bandwidth between the sensor, the memory and the processors to process the high frame rate data, and (iii) only output the images with any application specific data at the standard frame rate. Thus, off-chip data rate which is very important for the system cost is not increased although high frame rate sequences are used.

Figure 1.6: High frame rate capture – standard frame rate output.

Extending dynamic range and capturing motion blur-free images with this approach have been explored by several researchers [43, 44, 45, 46]. In those applications, video data at each pixel are processed temporally, independent of the neighboring pixels. This has limitations because the spatial information is not exploited. In this dissertation, we extend our high-frame-rate-capture/standard-frame-rate-output approach from 1D temporal processing to 3D spatio-temporal processing. This extension will enable more efficient implementations of several applications in video processing, computer vision and even image-based rendering. Moreover, it opens door to many new applications in those fields.

#### 1.3 Thesis organization

The dissertation discusses both the hardware and algorithmic aspects of video processing applications using high speed imagers and can thus be divided into two main parts. The first part, which includes Chapter 2 and 3, describes video processing applications enabled by high speed imaging capability of CMOS image sensors. The applications described follow the basic approach described in the previous section. The second part, which is Chapter 4, is on hardware and implementation issues. We present a DPS chip that demonstrates the high speed imaging capability of CMOS image sensor and then show that implementing a high speed imaging system on a single chip is feasible. We next briefly summarize of each chapter.

Chapter 2 describes a method for obtaining high accuracy optical flow estimates at a standard frame rate by capturing and processing a high frame rate version of the video and compare its performance to methods that only use standard frame rate sequences. We demonstrate significant performance improvements over conventional optical flow estimation that use standard frame rate image sequences.

Chapter 3 describes a method that uses a video sequence and accurate optical flow estimates to correct sensor gain Fixed Pattern Noise (FPN). The captured sequence and its optical flow are used to estimate gain FPN. Assuming brightness constancy along the motion trajectories, the pixels are grouped in blocks and each block's pixel gains are estimated by iteratively minimizing the sum of the squared brightness variations along the motion trajectories. Significant reductions in gain FPN are demonstrated using both real and synthetically generated video sequences with modest computational requirements.

Chapter 4 discusses the hardware implementation issues of the high-speed imaging system. On the sensor side, a  $352 \times 288$  pixel CMOS Digital Pixel Sensor chip with per-pixel single-slope ADC and 8-bit dynamic memory in a standard digital  $0.18\mu$ m CMOS process is described. The chip performs "snap-shot" image acquisition at continuous rate of 10,000 frames/s or 1 Gpixels/s. The chip demonstrates the high speed imaging capability of CMOS image sensors. We then discuss the limits on memory size and processing power that can be integrated with a CMOS image sensor in  $0.18\mu$ m process and below. We show that the integration of an entire video camera system on a chip is not only feasible at  $0.18\mu$ m process, but in fact underutilizes the possible on-chip processing power. Further, we argue that the onchip processing power and memory are sufficient to perform applications such as optical flow estimation by operating the sensor at high frame rate. As technology scales, applications that require even more processing power and memory such as tracking, pattern recognition, and 3D structure estimation may be implemented on a single chip.

Finally Chapter 5 concludes the thesis and discusses the most likely directions for future related research.

# Chapter 2

# **Optical Flow Estimation**

#### 2.1 Introduction

A key problem in the processing of video sequences is estimating the motion between video frames, often referred to as optical flow estimation (OFE). Once estimated, optical flow can be used in performing a wide variety of tasks such as video compression, 3-D surface structure estimation, super-resolution, motion-based segmentation and image registration. Optical flow estimation based on standard frame rate video sequences, such as 30 frames/s, has been extensively researched with several classes of methods developed including gradient-based, region-based matching, energy-based, Bayesian, and phase-based. Excellent survey papers that briefly describe several classes of methods and compare the performance of the methods can be found in [48, 49, 50].

There are several benefits of using high frame rate sequences for OFE. First, as frame rate increases, the intensity values along the motion trajectories vary less between consecutive frames when illumination level changes or occlusion occurs. Since many optical flow estimation methods explicitly or implicitly assume that intensity along motion trajectories stay constant [48, 49, 50], it is expected that using high frame rate sequences can enhance the estimation accuracy of these algorithms. Another important benefit is that as frame rate is increased the captured sequence exhibits less motion aliasing. Indeed large errors due to motion aliasing can occur even when using the best optical flow estimators. For example, when motion aliasing occurs a wagon wheel might appear to rotate backward even to a human observer when seen through devices such as movie screen and TV. This specific example is discussed in more detail in Section 2.3. There are many instances when the standard frame rate of 30 frames/s is not sufficient to avoid motion aliasing and thus incorrect optical flow estimates. Note that motion aliasing not only depends on the velocities but also on the spatial bandwidths. Thus, capturing sequences at a high frame rate not only helps when velocities are large but also for complex images with low velocities but high spatial bandwidths.

This chapter is organized as follows. In Section 2.2 we present a method [51, 52] for accurate optical flow estimation at a standard frame rate from a high frame rate version of the video sequence. This method is based on the well-known Lucas-Kanade algorithm [53]. Using synthetic input sequences generated by image warping of a still image, we also show significant improvements in accuracy attained using the proposed method. We then examine the memory and computational requirements of the proposed method. In Section 2.3 we give a brief review of 3-D spatio-temporal sampling theory and the analyze the effects of temporal sampling rate and motion aliasing on OFE. We present simulation results using sinusoidal input sequences showing that the minimum frame rate necessary to avoid motion aliasing. In Section 2.4 we discuss how the proposed method can be used with OFE algorithms other than the Lucas-Kanade algorithm. In particular, we extend the Haussecker algorithm [64] to work with high frame rate sequences and show that with this extension high accuracy optical flow estimates can be obtained even when brightness varies with time.

# 2.2 Optical flow estimation using high frame rate sequences

#### 2.2.1 Proposed method

In this subsection we present a method for obtaining high accuracy optical flow estimates at a standard frame rate by capturing and processing a high frame rate version of the video. The idea is to estimate optical flow at a high frame rate and then carefully integrate it temporally to estimate the optical flow between frames at the slower standard frame rate. Temporal integration, however, must be performed without losing the accuracy gained by using the high frame rate sequence. Obviously, if the temporal integration does not preserve the accuracy provided by the high frame rate sequence, then this approach would lose many of its benefits.

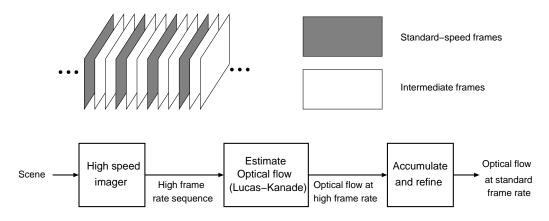

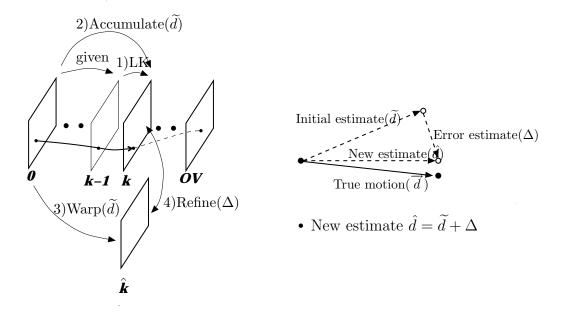

The block diagram of our proposed method is shown in Figure 2.1 for the case when the frame rate is 3 times the standard frame rate. We define OV as the oversampling factor (i.e., the ratio of the capture frame rate to the standard frame rate) and thus OV = 3 in the block diagram. Consider the sequence of high-speed frames beginning with a standard-speed frame (shaded frame in the figure) and ending with the following standard-speed frame. We first obtain high accuracy optical flow estimates between consecutive high-speed frames. These estimates are then used to obtain a good estimate of the optical flow between the two standard-speed frames.

We first describe how optical flow at a high frame rate is estimated. Although virtually any OFE method can be employed for this stage, we decided to use a gradientbased method since higher frame rate leads to reduced motion aliasing and better estimation of temporal derivatives, which directly improve the performance of such methods. In addition, because of the smaller displacements between consecutive frames in a high-speed sequence, smaller kernel sizes for smoothing and computing gradients can be used, which reduces the memory and computational requirements of the method.

Of the gradient-based methods, we chose the well known Lucas-Kanade's algorithm [53], which was shown to be among the most accurate and computationally

Figure 2.1: The block diagram of the proposed method (OV = 3).

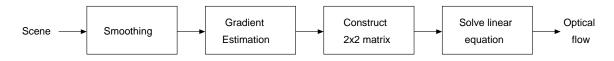

efficient methods for optical flow estimation [48]. A block diagram of the Lucas-Kanade OFE method is shown in Figure 2.2. Each frame is first pre-filtered using a spatio-temporal low pass filter to reduce aliasing and systematic error in the gradient estimates. The gradients  $i_x$ ,  $i_y$ , and  $i_t$  are typically computed using a 5-tap filter [48]. The velocity vector is then computed for each pixel (x, y) by solving the 2 × 2 linear equation

$$\begin{bmatrix} \sum w i_x^2 & \sum w i_x i_y \\ \sum w i_x i_y & \sum w i_y^2 \end{bmatrix} \begin{bmatrix} v_x \\ v_y \end{bmatrix} = -\begin{bmatrix} \sum w i_x i_t \\ \sum w i_y i_t \end{bmatrix}$$

Note that we have not included the spatial parameters (x, y) in the formulation to simplify notation. Here w(x, y) is a window function that assigns higher weight to the center of the neighborhood around (x, y) and the sums are typically over  $5 \times 5$ pixel neighborhoods.

Figure 2.2: Block diagram of Lucas-Kanade method. Note that the last three blocks are performed for each pixel of each frame.

After optical flow has been estimated at the high frame rate, we use it to estimate the optical flow at the standard frame rate. This is the third block of the block diagram in Figure 2.1. The key in this stage is to integrate optical flow temporally without losing the accuracy gained using the high frame rate sequences. A straightforward approach would be to simply accumulate the optical flow estimates between consecutive high-speed frames along the motion trajectories. The problem with this approach is that errors can accumulate with the accumulation of the optical flow estimates. To understand how errors can accumulate for a pixel, consider the diagram in Figure 2.3, where  $e_{k,l}$  is the magnitude of the OFE error vector between frames k and l. Assuming that  $\theta_k$ , the angles between the error vectors in the figure are random and uniformly distributed and that the mean squared magnitude of the OFE error between consecutive high-speed frames are equal, i.e.,  $E(e_{j-1,j}^2) = E(e_{0,1}^2)$ for  $j = 1, \ldots, k$ , the total mean-squared error is given by

$$E(e_{0,k}^2) = E(e_{0,k-1}^2) + E(e_{k-1,k}^2) - 2E(e_{k-1,k}e_{0,k-1}\cos\theta_k)$$

=  $\sum_{j=1}^k E(e_{j-1,j}^2) - 2\sum_{j=1}^k E(e_{j-1,j}e_{0,j-1}\cos\theta_j)$

=  $\sum_{j=1}^k E(e_{j-1,j}^2) = kE(e_{0,1}^2),$

which grows linearly with k. On the other hand, if the optical flow estimation errors are systematic, i.e., line up from one frame to the next, and their magnitudes are temporally independent, which yields  $E(e_{j-1,j}e_{l-1,l}) = E(e_{j-1,j})E(e_{l-1,l})$ , then the total mean-squared error is given by

$$E[e_{0,k}^2] = E[e_{0,k-1}^2 + e_{k-1,k}^2 + 2e_{k-1,k}e_{0,k}] = E[(e_{0,k-1} + e_{k-1,k})^2]$$

=  $E[(\sum_{j=1}^k e_{j-1,j})^2] = k^2 E[e_{0,1}^2],$

which grows quadratically with k. In practice, the optical flow estimation error was shown to have a random component and a non-zero systematic component by several

$$e_{0,k-1} \bigvee_{k=0,k}^{e_{k-1,k}} e_{0,k}^2 = e_{0,k-1}^2 + e_{k-1,k}^2 - 2e_{k-1,k}e_{0,k} \cos \theta_k$$

Figure 2.3: The accumulation of error vectors when accumulating optical flow without using refinement.

researchers [54, 55, 56, 57], and as a result, the mean-squared error  $E[e_{0,k}^2]$  is expected to grow faster than linear but slower than quadratic in k.

To prevent this error accumulation, we add a refinement (or correction) stage after each iteration (see Figure 2.4). We obtain frame  $\hat{k}$  by warping frame 0 according to our accumulated optical flow estimate  $\tilde{d}$ , and assume that frame k is obtained by warping frame 0 according to the true motion between the two frames, (which we do not know). By estimating the displacement between frames k and  $\hat{k}$ , we can estimate the error between the true flow and the initial estimate  $\tilde{d}$ . In the refinement stage, we estimate this error and add it to the accumulated optical flow estimate. Although the estimation of the error is not perfect, we found that it significantly reduces error accumulation.

A description of the proposed method is given below. Consider OV + 1 high-speed frames beginning with a standard-speed output frame and ending with the following one. Number the frames  $0, 1, \ldots, OV$  and let  $\hat{d}_{k,l}$  be the estimated optical flow (displacement) from frame k to frame l, where  $0 \le k \le l \le OV$ . The end goal is to estimate the optical flow between frames 0 and OV, i.e.,  $\hat{d}_{0,OV}$ .

Proposed method:

- 1. Capture a standard-speed frame, set k = 0.

- 2. Capture the next high-speed frame and set k = k + 1.

- 3. Estimate  $\hat{d}_{k-1,k}$  using Lucas-Kanade method.

Figure 2.4: Accumulate and refine stage.

- 4.  $\tilde{d}_{0,k} = \hat{d}_{0,k-1} + \hat{d}_{k-1,k}$  where addition of optical flow estimates are along the motion trajectories.

- 5. Estimate  $\Delta_k$ , the displacement between frame k and  $\hat{k}$ .

- 6. Set refined estimate  $\hat{d}_{0,k} = \tilde{d}_{0,k} + \Delta_k$ .

- 7. Repeat steps 2 through 6 until k = OV

- 8. Output  $\hat{d}_{0,OV}$  the final estimate of optical flow at the standard frame rate

Since the proposed algorithm is iterative, its memory requirement is independent of frame rate. Furthermore, since it uses 2-tap temporal filter for smoothing and estimating temporal gradients, its memory requirement is less than that of the conventional Lucas-Kanade method, which typically uses a 5-tap temporal filter. Assuming an  $M \times N$  image, our method requires approximately 190MN(OV) operations per frame and 12MN bytes of frame memory. By comparison the standard Lucas-Kanade method as implemented by Barron *et al.* [48] requires 105MN operations per frame and 16MN bytes of frame memory.

#### 2.2.2 Simulation and results

In this subsection, we describe the simulations we performed using synthetically generated natural image sequences to test our optical flow estimation method. To evaluate the performance of the proposed method and compare with methods using standard frame rate sequences, we need to compute the optical flow using both the standard and high frame rate versions of the same sequence, and then compare the estimated optical flow in each case to the true optical flow. We use synthetically generated video sequences obtained by warping of a natural image. The reason for using synthetic sequences, instead of real video sequences, is that the amount of displacement between consecutive frames can be controlled and the true optical flow can be easily computed from the warping parameters.

We use a realistic image sensor model [60] that incorporates motion blur and noise in the generation of the synthetic sequences, since these effects can vary significantly as a function of frame rate, and can thus affect the performance of optical flow estimation. In particular, high frame rate sequences have less motion blur but suffer from lower SNR, which adversely affects the accuracy of optical flow estimation. The image sensor in a digital camera comprises a 2-D array of pixels. During capture, each pixel converts incident photon flux into photocurrent. Since the photocurrent density j(x, y, t) A/cm<sup>2</sup> is too small to measure directly, it is spatially and temporally integrated onto a capacitor in each pixel and the charge q(m, n) is read out at the end of exposure time T. Ignoring dark current, the output charge from a pixel can be expressed as

$$q(m,n) = \int_0^T \int_{ny_0}^{ny_0+Y} \int_{mx_0}^{mx_0+X} j(x,y,t) dx dy dt + N(m,n),$$

(2.1)

where  $x_0$  and  $y_0$  are the pixel dimensions, X and Y are the photodiode dimensions, (m, n) is the pixel index, and N(m, n) is the noise charge. The noise is the sum of two independent components, shot noise and readout noise. The spatial and temporal integration results in low pass filtering that can cause motion blur. Note that the pixel intensity i(m, n) commonly used in image processing literature is directly proportional to the charge q(m, n). The steps of generating a synthetic sequence are as follows.

- 1. Warp a high resolution  $(1312 \times 2000)$  image using perspective warping to create a high resolution sequence.

- 2. Spatially and temporally integrate (according to Equation (1)) and subsample the high resolution sequence to obtain a low resolution sequence. In our example, we subsampled by factors of  $4 \times 4$  spatially and 10 temporally to obtain each high-speed frame.

- 3. Add readout noise and shot noise according to the model.

- 4. Quantize the sequence to 8 bits/pixel.

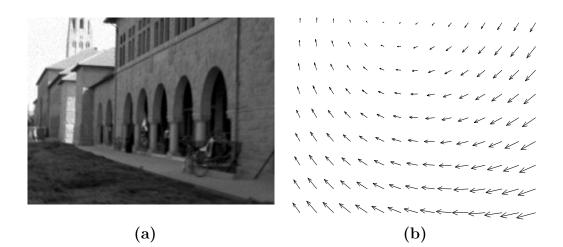

Three different scenes derived from a natural image (Figure 2.5) were used to generate the synthetic sequences. For each scene, two versions of each video, one captured at a standard frame rate (OV = 1) and the other captured at four times the standard frame rate (OV = 4), are generated as described above. The maximum displacements were between 3 and 4 pixels/frame at the standard frame rate. We performed optical flow estimation on the (OV = 1) sequences using the standard Lucas-Kanade method as implemented by Barron *et al.* [48] and on the (OV = 4) sequences using the proposed method. Both methods generate optical flow estimates at a standard frame rate of 30 frames/s. Note that the standard Lucas-Kanade method was implemented using 5-tap temporal filters for smoothing and estimating temporal gradients while the proposed method used 2-tap temporal filters. The resulting average angular errors between the true and the estimated optical flows are given in Table 2.1. The densities of all estimated optical flows are close to 50%.

The results demonstrate that using the proposed method in conjunction with the high frame rate sequence can achieve higher accuracy. Note that the displacements were kept relatively small (as measured at the standard frame rate) to make comparison between the two methods more fair. As displacements increase, the accuracy of the standard Lucas-Kanade method deteriorates rapidly and hierarchical methods should be used in the comparison instead. On the other hand, the proposed method is much more robust to large displacements because of the higher sampling rate.

Figure 2.5: (a) One frame of a test sequence and (b) its known optical flow.

|       | Lucas-Kana                     | ade method at   | Proposed method using               |                 |

|-------|--------------------------------|-----------------|-------------------------------------|-----------------|

| Scene | standard frame rate $(OV = 1)$ |                 | high frame rate sequence $(OV = 4)$ |                 |

| Scene | Angular error                  | Magnitude error | Angular error                       | Magnitude error |

| 1     | 4.43°                          | 0.24            | $3.43^{\circ}$                      | 0.14            |

| 2     | 3.94°                          | 0.24            | $2.91^{\circ}$                      | 0.17            |

| 3     | $4.56^{\circ}$                 | 0.32            | $2.67^{\circ}$                      | 0.17            |

Table 2.1: Average angular error and magnitude error using Lucas-Kanade method with standard frame rate sequences versus the proposed method using high frame rate sequences.

To investigate the gain in accuracy of the proposed method for large displacements, we applied the Lucas-Kanade method, our proposed method with OV = 10, and the hierarchical matching-based method by Anandan [61] as implemented by Barron [48] to a synthetic sequence. The maximum displacement was 10 pixels/frame at the standard frame rate. The average angular errors and magnitude errors of the estimated optical flows are given in Table 2.2. For comparison, we calculated average errors for Anandan's method at locations where Lucas-Kanade method gave valid optical flow, although Anandan's method can provide 100% density. Thus, values in the table were calculated where the densities of all estimated optical flows are close to 50%.

|                             | Angular error  | Magnitude error |

|-----------------------------|----------------|-----------------|

| Lucas-Kanade method         | 9.18°          | 1.49            |

| Anandan's method            | $4.72^{\circ}$ | 0.53            |

| Proposed method $(OV = 10)$ | $1.82^{\circ}$ | 0.21            |

Table 2.2: Average angular and magnitude error using Lucas-Kanade, Anandan's and proposed method.

### 2.3 Effect of motion aliasing on optical flow estimation

This section reviews 3-D spatio-temporal sampling theory and investigates the effect of motion aliasing on the accuracy of optical flow estimation. We hypothesize that the minimum frame rate necessary to achieve good performance is largely determined by the minimum frame rate necessary to prevent motion aliasing in the sequence. This is supported in Subsection 2.3.2 through simulation results using the proposed method.

#### 2.3.1 Review of spatio-temporal sampling theory

A simplified but highly insightful example of motion is that of global motion with constant velocity in the image plane. Assuming that intensity values are constant along the motion trajectories without any occlusion, the pixel intensity is given by

$$i(x, y, t) = i(x - v_x, y - v_y, 0)$$

=  $i_0(x - v_x, y - v_y),$

where  $i_0(x, y)$  denotes the 2-D pixel intensity for t = 0 and  $v_x$  and  $v_y$  are the global velocities in the x and y directions, respectively. This is commonly assumed either globally or locally in many applications such as motion-compensated standards conversion and video compression. After taking the Fourier transform, we obtain

$$I(f_x, f_y, f_t) = I_0(f_x, f_y) \cdot \delta(f_x v_x + f_y v_y + f_t),$$

where  $I_0(f_x, f_y)$  is the 2-D Fourier transform of  $i_0(x, y)$  and  $\delta(\cdot)$  is the 1-D Dirac delta function. Thus, it is clear that the energy of  $I(f_x, f_y, f_t)$  is confined to a plane given by  $f_x v_x + f_y v_y + f_t = 0$ . If we assume that  $i_0(x, y)$  is bandlimited such that  $I(f_x, f_y) = 0$  for  $|f_x| > B_x$  and  $|f_y| > B_y$ , then i(x, y, t) is bandlimited temporally as well, i.e,  $I(f_x, f_y, f_t) = 0$  for  $|f_t| > B_t$  where  $B_t = B_x v_x + B_y v_y$ . Note that the temporal bandwidth depends on both the spatial bandwidths and the spatial velocities.

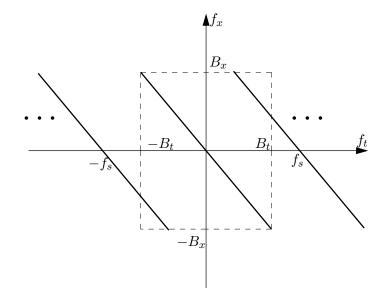

To simplify our discussion, we assume in the following that sampling is performed only along the temporal direction and that the spatial variables are taken as continuous variables (no sampling along the spatial directions). While this may initially seem somewhat strange, it greatly simplifies the analysis, and interestingly is not entirely unrealistic, since it is analogous to the shooting of motion picture film, where each film frame corresponds to a temporal sample of the video. Figure 2.6 shows the spatio-temporal spectrum of video when sampled only in the temporal direction. For simplicity of illustration, we consider its projection onto the  $(f_x, f_t)$ -plane, where the support can be simplified to  $f_x v_x + f_t = 0$ . Each line represents the spatio-temporal support of the sampled video sequence.

Figure 2.6: Spatio-temporal spectrum of a temporally sampled video.

Let us consider the problem of how fast we should sample the original continuous video signal along the temporal dimension such that it can be perfectly recovered from its samples. Assume that an ideal lowpass filter with rectangular support in the 3-D frequency domain is used for reconstruction, although in certain ideal cases, a sub-Nyquist sampled signal can also be reconstructed by an ideal motioncompensated reconstruction filter assuming the replicated spectra do not overlap (see [50] for details). To recover the original continuous spatio-temporal video signal from its temporally sampled version, it is clear from the figure that the temporal sampling frequency (or frame rate)  $f_s$  must be greater than  $2B_t$  in order to avoid aliasing in the temporal direction. If we assume global motion with constant velocity  $v_x$  and  $v_y$ (in pixels per standard-speed frame) and spatially bandlimited image with  $B_x$  and  $B_y$ as the horizontal and vertical spatial bandwidths (in cycles per pixel), the minimum temporal sampling frequency  $f_{s,Nyq}$  to avoid motion aliasing is given by

$$f_{s,Nyq} = 2B_t = 2B_x v_x + 2B_y v_y, \tag{2.2}$$

where  $f_{s,Nyq}$  is in cycles per standard-speed frame. Note that the temporal sampling frequency in cycles per standard-speed frame is the oversampling factor OV. Moreover, since OV is an integer in our framework to ensure that standard-speed frames correspond to a captured high-speed frame (see Figure 2.1), the minimum oversampling factor to avoid motion aliasing,  $OV_{\text{theo}}$ , can be represented as

$$OV_{\text{theo}} = \lceil f_{\text{s,Nyq}} \rceil$$

$$= \lceil 2B_x v_x + 2B_y v_y \rceil$$

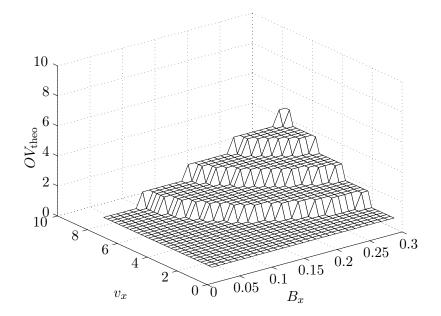

To illustrate this relationship consider the simple case of a sequence with only global motion in the horizontal direction (i.e., with  $v_y = 0$ ). Figure 2.7 plots  $OV_{\text{theo}} = [2B_x v_x]$  versus horizontal velocity and spatial bandwidth for this case.

Figure 2.7: Minimum OV to avoid motion aliasing, as a function of horizontal velocity  $v_x$  and horizontal spatial bandwidth  $B_x$ .

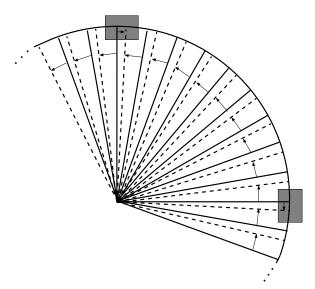

Motion aliasing adversely affects the performance of optical flow estimation even as perceived by the human visual system. This is illustrated by the classic example of a rotating wagon wheel (see Figure 2.8). In this example the wagon wheel is rotating counter-clockwise and we wish to estimate its motion from two frames captured at times t = 0 and t = 1. The solid lines represent positions of the wheel and spokes at t = 0 and the dashed lines represent the positions at t = 1. Optical flow is locally estimated for the two shaded regions of the image in Figure 2.8. As can be seen, the optical flow estimates are in the *opposite* direction of the true motion (as often experienced by a human observer watching through display devices such as TVs and projectors). The wheel is rotating counter-clockwise, while the optical flow estimates from the local image regions would suggest that it is rotating clockwise. This ambiguity is caused by insufficient temporal sampling and the fact that optical flow estimation (and the human visual system) implicitly assume the smallest possible displacements (corresponding to a lowpass filtering of the possible motions).

Figure 2.8: Wagon wheel rotating counter-clockwise illustrating motion aliasing from insufficient temporal sampling: the local image regions (gray boxes) appear to move clockwise.

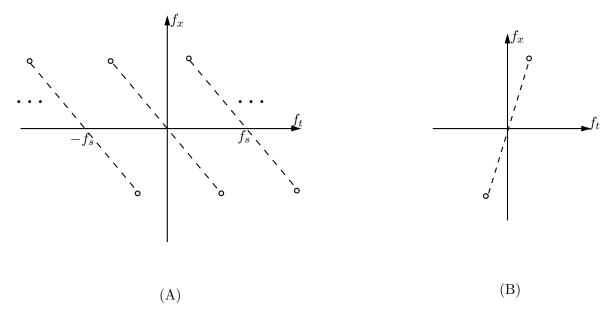

Let us consider the spatio-temporal frequency content of the local image regions in Figure 2.8. Since each shaded region has a dominant spatial frequency component and the assumption of global velocity for each small image region [48] holds, its spatio-temporal frequency diagram can be plotted as shown in Figure 2.9 (A). The circles represent the frequency content of a sinusoid and the dashed lines represent the plane where most of the energy resides. Note that the slope of the plane is inversely proportional to the negative of the velocity. The spatio-temporal frequency content of the baseband signal after reconstruction by the OFE algorithm is plotted in Figure 2.9 (B). As can be seen aliasing causes the slope at which most of the energy resides to not only be different in magnitude, but also to have a different sign, corresponding to motion in the opposite direction. This example shows that motion aliasing can cause incorrect motion estimates for any OFE algorithm. To overcome motion aliasing, one must either sample sufficiently fast, or have prior information about the possible motions as in the case of the moving wagon wheel, where the human observer makes use of the direction of motion of the wagon itself to correct the misperception about the rotation direction of the wheel.

Figure 2.9: Spatio-temporal diagrams of, (A) the shaded region in Figure 2.8 and (B) its baseband signal.

#### 2.3.2 Simulation and results

In this subsection we discuss simulation results using sinusoidal test sequences and the synthetically generated natural image sequence used in Subsection 2.2.2. The reason for using sinusoidal sequences is to assess the performance of the proposed method as spatial frequency and velocity are varied in a controlled manner. As discussed in the previous subsection, motion aliasing depends on both the spatial frequency and the velocity and can have a detrimental effect on optical flow estimation. Using a natural sequence, it would be difficult to understand the behavior of the proposed method estimates optical flow by performing spatially local operations. In addition, typical figures of merit, such as average angular error and average magnitude error, would be averaged out across the frame. The use of sinusoidal test sequences can overcome these problems and can enable us to find the minimum OV needed to obtain a desired accuracy, which can then be used to select the minimum high-speed frame rate for a natural scene.

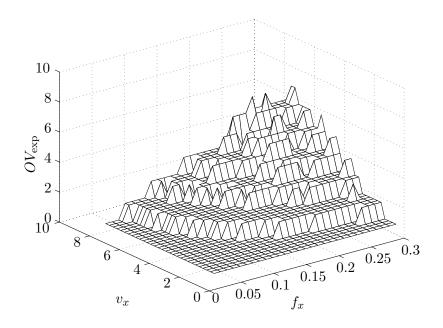

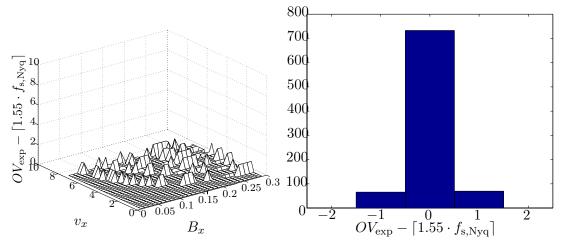

We considered a family of 2-D sinusoidal sequences with equal horizontal and vertical frequencies  $f_x = f_y$  moving only in the horizontal direction at speed  $v_x$  (i.e.,  $v_y = 0$ ). For each  $f_x$  and  $v_x$ , we generated a sequence with OV = 1 and performed optical flow estimation using the proposed method. We then incremented OV by 1 and repeated the simulation. We noticed that the average error drops rapidly beyond a certain value of OV and that it remained relatively constant for OVs higher than that value. Based on this observation we defined the minimum oversampling ratio  $OV_{exp}$  as the OV value at which the magnitude error drops below a certain threshold. In particular, we chose the threshold to be 0.1 pixels/frame. Once we found the minimum value of OV, we repeated the experiment for different spatial frequencies and velocities. The results are plotted in Figure 2.10.

Recall the discussion in the previous subsection (including Figure 2.7) on the minimum oversampling factor as a function of spatial bandwidth and velocity needed to avoid motion aliasing. Note the similarity between the theoretical results in Figure 2.7 and their experimental counterpart in Figure 2.10. This is further illustrated by the

Figure 2.10: Minimum OV as a function of horizontal velocity  $v_x$  and horizontal spatial frequency  $f_x$ .

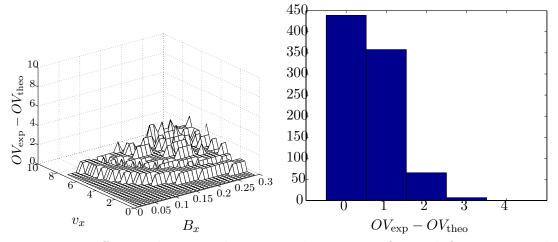

plot of their difference and its histogram in Figure 2.11. This similarity supports our hypothesis that reduction in motion aliasing is one of the most important benefits of using high frame rate sequences. The difference in Figure 2.11 can be further reduced by sampling at a higher rate than  $[f_{s,Nyq}]$  to better approximate brightness constancy and improve the estimation of temporal gradients. It has been shown that gradient estimators using a small number of taps suffer from poor accuracy when high frequency content is present [58, 59]. In our implementation, we used a 2-tap temporal gradient estimator, which performs accurately for temporal frequencies  $f_t < \frac{1}{3}$  as suggested in [58]. Thus we need to sample at a rate higher than 1.5 times the Nyquist temporal sampling rate. Choosing an OV curve that is 1.55 times the Nyquist rate (i.e.,  $[1.55f_{s,Nyq}]$ ), in Figure 2.12 we plot the difference between the  $OV_{exp}$  curve in Figure 2.10 and the OV curve. Note the reduction in the difference achieved by the increase in frame rate.

Figure 2.11: Difference between the empirical minimum OV and OV corresponding to the Nyquist rate.

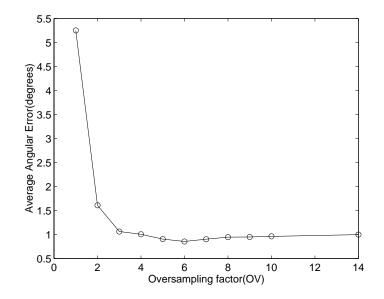

We also investigated the effect of varying OV and motion aliasing on accuracy using the synthetically generated image sequences presented in Subsection 2.2.2. Figure 2.13 plots the average angular error of the optical flow estimates using the proposed method for OV between 1 and 14. The synthetic test sequence had a global displacement of 5 pixels/frame at OV = 1. As OV was increased, motion aliasing

Figure 2.12: Difference between the empirical minimum OV and OV corresponding to the 1.55 times the Nyquist rate.

and the error due to temporal gradient estimation decreased, leading to higher accuracy. The accuracy gain resulting from increasing OV, however, levels off as OV is further increased. This is caused by the decrease in sensor SNR due to the decrease in exposure time and the leveling off of the reduction in motion aliasing. For this example sequence, the minimum error is achieved at OV = 6, where displacements between consecutive high-speed frames are approximately 1 pixel/frame.

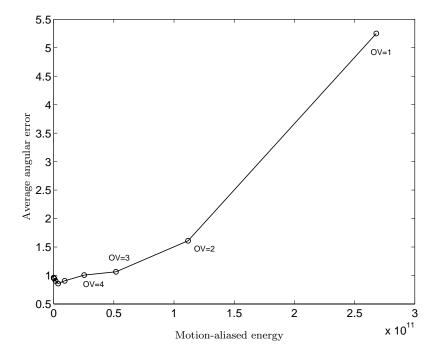

To investigate the effect of motion aliasing, we also estimated the energy in the image that leads to motion aliasing. Note that since the sequence has global motion with constant velocity, the temporal bandwidth of the sequence can be estimated as  $B_t = 5B_x + 5B_y$  by assuming the knowledge of initial estimates of  $v_x = v_y = 5$  pixels/frame. Thus, motion aliasing occurs for spatial frequencies  $\{f_x, f_y\}$  that satisfy the constraint  $f_x + f_y > OV/10$ . By using 2D-DFT of the first frame and this constraint, we calculated the energy in the sequence that is motion aliased for different OVs. Figure 2.14 plots the average angular error versus the energy that is motion aliased. Each point corresponds to an OV value and it is clear that the performance of the proposed OFE method is largely influenced by the presence of motion aliasing.

This confirms our hypothesis that motion aliasing significantly affects the performance of optical flow estimation and that a key advantage of high frame rate is the

Figure 2.13: Average angular error versus oversampling factor (OV).

Figure 2.14: Average angular error versus energy in the image that leads to motion aliasing.

reduction of motion aliasing. Also, this example shows that with initial estimates of velocities, we can predict the amount of energy in the image that will be aliased. This can be used to identify the necessary frame rate to achieve high accuracy optical flow estimation for a specific scene.

## 2.4 Extension to handle brightness variation

In the previous sections we described and tested a method for obtaining high accuracy optical flow at a standard frame rate using a high frame rate sequence. We used the Lucas-Kanade method to estimate optical flow at high frame rate and then accumulated and refined the estimates to obtain optical flow at standard frame rate. The Lucas-Kanade method assumes brightness constancy, and although high frame rate makes this assumption more valid, in this section we show that brightness variations can be handled more effectively using other estimation methods. Specifically, we show that by using an extension of the Haussecker [64] method, temporal oversampling can benefit optical flow estimation even when brightness constancy assumption does not hold.

There have been many proposals of how to handle the case when the brightness constancy assumption does not hold [64, 62, 63, 65, 66, 67, 68]. It has been shown that a linear model with offset is sufficient to model brightness variation in most cases [62, 63, 68]. For example, Negahdaripour *et al.* developed an OFE algorithm based on this assumption and demonstrated good performance [62, 63]. Haussecker *et al.* developed models for several cases of brightness variation and described a method for coping with them [64]. We will use Haussecker's framework with the assumption of linear brightness variation for estimating optical flow at high frame rate.

#### 2.4.1 Review of models for brightness variation

We begin with a brief summary of the framework described in [64]. The brightness change is modeled as a parameterized function h, i.e.,

$$i(\mathbf{x}(t),t) = h(i_0,t,\mathbf{a}),$$

where  $\mathbf{x}(t)$  denotes the path along which brightness varies,  $i_0 = i(\mathbf{x}(0), 0)$  denotes the image at time 0, and **a** denotes a *Q*-dimensional parameter vector for the brightness change model. The total derivative of both sides of this equation yields

$$(\nabla i)^T \mathbf{v} + i_t = f(i_0, t, \mathbf{a}), \tag{2.3}$$

where f is defined as

$$f(i_0, t, \mathbf{a}) = \frac{\mathrm{d}}{\mathrm{d}t} [h(i_0, t, \mathbf{a})].$$

Note that when brightness is constant, f = 0 and Equation 2.3 simplifies to the conventional brightness constancy constraint. The goal is to estimate the parameters of the optical flow field **v** and the parameter vector **a** of the model f. Remembering that  $h(i_0, t, \mathbf{a} = \mathbf{0}) = i_0$ , we can expand h using the Taylor series around  $\mathbf{a} = \mathbf{0}$  to obtain

$$h(i_0, t, \mathbf{a}) \approx i_0 + \sum_{k=1}^Q a_k \frac{\partial h}{\partial a_k}.$$

Thus, f can be written as a scalar product of the parameter vector **a** and a vector containing the partial derivatives of f with respect to the parameters  $a_k$ , i.e.,

$$f(i_0, t, \mathbf{a}) = \sum_{k=1}^{Q} a_k \frac{\partial f}{\partial a_k} = (\nabla_{\mathbf{a}} f)^T \mathbf{a}.$$

(2.4)

Using Equation 2.4, Equation 2.3 can be expressed as

$$\mathbf{c}^T \mathbf{p}_h = \mathbf{0},$$

where

$$\mathbf{c} = [(\nabla_{\mathbf{a}} f)^T, (\nabla i)^T, i_t]^T$$

$$\mathbf{p}_h = [-\mathbf{a}^T, \mathbf{v}^T, 1]^T.$$

Here, the (Q + 3)-dimensional vector  $\mathbf{p}_h$  contains the flow field parameters and the brightness parameters of h. The vector  $\mathbf{c}$  combines the image derivative measurements

and the gradient of f with respect to **a**. To solve for  $\mathbf{p}_h$ , we assume that  $\mathbf{p}_h$  remains constant within a local space-time neighborhood of N pixels. The constraints from the N pixels in the neighborhood can be expressed as

$$\mathbf{G}\mathbf{p}_h = 0$$

where  $\mathbf{G} = [\mathbf{c}_1, ..., \mathbf{c}_N]^T$ . The estimate of  $\mathbf{p}_h$  can be obtained by a total least squares (TLS) solution.

#### 2.4.2 Using Haussecker method with high frame rate

We assume a linear model with offset for brightness variation which yields  $f = a_1 + a_2i_0$ . We use Haussecker's method to estimate  $v_x, v_y, a_1$  and  $a_2$  for every high-speed frame. We then accumulate and refine  $v_x, v_y, a_1$  and  $a_2$  in a similar manner to the method described in Section 2.2 to obtain optical flow estimates at a standard frame rate.

The parameters  $v_x$  and  $v_y$  are accumulated and refined exactly as before, and we now describe how to accumulate and refine  $a_1$  and  $a_2$  along the motion trajectories. To accumulate  $a_1$  and  $a_2$ , we first define  $\hat{a}_{1(k,l)}$  and  $\hat{a}_{2(k,l)}$  to be the estimated brightness variation parameters between frames k and l along the motion trajectory. We estimate  $\hat{a}_{1(k-1,k)}$  and  $\hat{a}_{2(k-1,k)}$  and assume that  $\hat{a}_{1(0,k-1)}$  and  $\hat{a}_{2(0,k-1)}$  are available from the previous iteration. Since  $f = a_1 + a_2i_0$ , we model the brightness variation such that

$$i_{k-1} - i_0 = \hat{a}_{1(0,k-1)} + \hat{a}_{2(0,k-1)}i_0$$

$$i_k - i_{k-1} = \hat{a}_{1(k-1,k)} + \hat{a}_{2(k-1,k)}i_{k-1},$$

for each pixel in frame 0, where  $i_k$  is the intensity value for frame k along the motion trajectory. By arranging the terms and eliminating  $i_{k-1}$ , we can express  $i_k$  in terms of  $i_0$  such that

$$i_k = \hat{a}_{1(k-1,k)} + (1 + \hat{a}_{2(k-1,k)})(\hat{a}_{1(0,k-1)} + (1 + \hat{a}_{2(0,k-1)})i_0).$$

$$(2.5)$$

Let  $\tilde{a}_{1(0,k)}$  and  $\tilde{a}_{2(0,k)}$  denote the accumulated brightness variation parameters between frames 0 and k along the motion trajectory. Therefore, by definition,  $i_k = \tilde{a}_{1(0,k)} + (1 + \tilde{a}_{2(0,k)})i_0$  and by comparing this equation with Equation 2.5, accumulated brightness variation parameters are obtained by

$$\tilde{a}_{1(0,k)} = \hat{a}_{1(k-1,k)} + (1 + \hat{a}_{2(k-1,k)})\hat{a}_{1(0,k-1)}

\tilde{a}_{2(0,k)} = \hat{a}_{2(k-1,k)} + (1 + \hat{a}_{2(k-1,k)})\hat{a}_{2(0,k-1)}.$$

Frame  $\hat{k}$  is obtained by warping frame 0 according to our initial estimate of optical flow between frames 0 and k and changing the brightness according to  $\tilde{a}_{1(0,k)}$  and  $\tilde{a}_{2(0,k)}$ , i.e.,

Frame

$$k = (1 + \tilde{a}_{2(0,k)})i_k(x - \tilde{v}_{x(0,k)}, y - \tilde{v}_{y(0,k)}) + \tilde{a}_{1(0,k)},$$

where  $\tilde{v}_{x(0,k)}$  and  $\tilde{v}_{y(0,k)}$  are the accumulated optical flow estimates between frames 0 and k. By estimating the optical flow and brightness variation parameters between original frame k and motion-compensated frame  $\hat{k}$ , we can estimate the error between the true values and the initial estimates obtained by accumulating. For the optical flow, we estimate the error and add it to our initial estimate, whereas for the brightness variation parameters, we perform the refinement as

$$\hat{a}_{1(0,k)} = a_{1\Delta} + (1 + a_{2\Delta})\tilde{a}_{1(0,k)}$$

$$\hat{a}_{2(0,k)} = a_{2\Delta} + (1 + a_{2\Delta})\tilde{a}_{2(0,k)},$$

where  $a_{1\Delta}$  and  $a_{2\Delta}$  are the brightness variation parameters between frames k and  $\hat{k}$ . The accumulation and refinement stage is repeated until we have the parameters between frames 0 and OV.

We tested this method using the sequences described in Subsection 2.2.2 but with global brightness variations. In these sequences, however, the global brightness changed with  $a_{1(0,OV)} = 5$  and  $a_{2(0,OV)} = 0.1$ . We performed optical flow estimation on the OV = 1 sequences using the Haussecker's method and on the OV = 4 sequences using our extended method. The resulting average angular errors and magnitude

| Scene | Haussecker's method $(OV = 1)$ |                 | The proposed method $(OV = 4)$ |                 |

|-------|--------------------------------|-----------------|--------------------------------|-----------------|

|       | Angular error                  | Magnitude error | Angular error                  | Magnitude error |

| 1     | $5.12^{\circ}$                 | 0.25            | 3.33°                          | 0.15            |

| 2     | 6.10°                          | 0.32            | $2.99^{\circ}$                 | 0.18            |

| 3     | $7.72^{\circ}$                 | 0.54            | $2.82^{\circ}$                 | 0.18            |

errors between the true and the estimated optical flows are given in Table 2.3.

Table 2.3: Average angular error and magnitude error using Haussecker's method with OV = 1 sequences versus proposed extended method with OV = 4 sequences.

These results demonstrate that using high frame rate, high accuracy optical flow estimates can be obtained even when brightness varies with time, i.e., when brightness constancy assumption does not hold. Furthermore, with this extension, we have also demonstrated that our proposed method can be used with OFE algorithms other than the Lucas-Kanade algorithm.

## 2.5 Summary

In this chapter, we described a method for improving the optical flow estimation accuracy for video at a conventional standard frame rate, by initially capturing and processing the video at a higher frame rate. The method begins by estimating the optical flow between frames at the high frame rate, and then accumulates and refines these estimates to produce accurate estimates of the optical flow at the desired standard frame rate. The method was tested on synthetically generated video sequences and the results demonstrate significant improvements in OFE accuracy. Also, with sinusoidal input sequences, we showed that reduction of motion aliasing is an important potential benefit of using high frame rate sequences. We also described methods to estimate the required oversampling rate to improve the optical flow accuracy, as a function of the velocity and spatial bandwidth of the scene. The proposed method can be used with other OFE algorithms besides the Lucas-Kanade algorithm. For example, we began with the Haussecker algorithm, designed specifically for optical flow estimation when the brightness varies with time, and extended it with the proposed method to work on high frame rate sequences. Furthermore, we demonstrated that our extended version provides improved accuracy in optical flow estimation as compared to the original Haussecker algorithm operating on video captured at the standard frame rate.

# Chapter 3

# Gain Fixed Pattern Noise Correction

# 3.1 Introduction

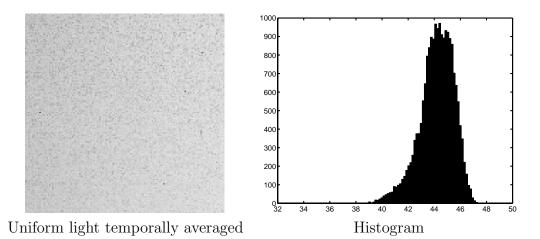

Most image sensors have linear transfer function such that the pixel intensity value i as a function of its input signal s, e.g., photocurrent density [60], can be expressed as

$$i = hs + i_{os},\tag{3.1}$$

where h is the gain factor and  $i_{os}$  is the offset, which includes the dark signal as well as the offset due to the amplifiers and buffers. Since all the pixels do not have the same gain h and offset  $i_{os}$ , image data read out of the image sensor pixel array are not uniform even under uniform illumination. Figure 3.1 illustrates an image (with its histogram) obtained by capturing 100 frames under uniform illumination and averaging them to significantly reduce the temporal noise. Note that the image has spatial variation even when there is little temporal noise. Fixed pattern noise (FPN) is this spatial variation of output pixel values under uniform illumination. FPN is caused by variations in pixel gains and offsets due to device mismatches and process parameter variations across an image sensor. It is a major source of image quality degradation especially in CMOS image sensors [72, 73]. In a CCD sensor, since all pixels share the same output amplifier, FPN is mainly due to variations in photodetector area and dark current. In a CMOS image sensor, however, pixels are read out over different chains of buffers and amplifiers each with different gain and offset, resulting in relatively high FPN.

Figure 3.1: An image and its histogram of uniform illumination illustrating FPN

FPN can be divided into offset FPN and gain FPN. Offset FPN is due to pixel to pixel variations in  $i_{os}$  and can be significantly reduced by correlated-double sampling (CDS). CDS first captures a frame with no exposure time (immediately after pixel reset) and then subtracts it off the desired frame with proper exposure time. Gain FPN is caused by variations in the gain factor h. While offset FPN can be significantly reduced using correlated double sampling (CDS), no method exists for effectively reducing gain FPN. In [74] a method is proposed for reducing gain FPN by characterizing the sensor's pixel gains after manufacture and storing the gains in a lookup table that is subsequently used to perform the correction. A problem with this method is that gain FPN changes with temperature and aging, making a "static" gain lookup table approach inaccurate. Another method would be to characterizing gain FPN requires many captures at different uniform illuminations.

In this chapter, we present a method to estimate and correct gain FPN using a video sequence and its optical flow. This method can be used in digital video or still cameras without requiring multiple captures of uniformly illuminated scenes at different intensities [70, 71]. The key idea of the method is to assume brightness constancy along the motion trajectories and use this information to estimate the gains for each pixel. For example, when a light intensity patch falls on a pixel at t = 0and on another pixel at t = 1, we can estimate the ratio of the gains at these two pixels. By gathering the ratio of gains for all the pixels in the image sensor and for multiple frames, we can estimate the gain for all the pixels in the image sensor. Since this method tracks the intensity variations along the motion trajectories due to gain FPN, it requires global motion between frame which needs to be estimated before this method is applied. Note that the required motion in the scene can be provided by simply panning the camera during capture.

In the following section, we describe the image and FPN model used throughout the chapter. In Section 3.3, we describe our algorithm for estimating and correcting gain FPN and illustrate its operation via simple 1D examples. In Section 3.4, we show simulation results using a synthetically generated sequence and its optical flow. We then show experimental results using a real video sequence taken with our experimental imaging system [75].

## 3.2 Image and fixed pattern noise model

In this chapter, we only consider gain FPN and assume that offset FPN has been canceled with CDS. After eliminating the offset term in Equation 3.1 and including gain variations, we obtain

$$\begin{split} i(x,y,t) &= i_0(x,y,t) + \Delta i(x,y,t) \\ &= (h_0 + \Delta h(x,y)) s(x,y,t) \\ &= (1 + \frac{\Delta h(x,y)}{h_0}) i_0(x,y,t) \\ &= a(x,y) i_0(x,y,t), \end{split}$$

where  $i_0(x, y, t)$  is the ideal intensity value at pixel (x, y) and time (frame) t,  $h_0$  is the nominal gain factor, and  $\Delta h(x, y)$  is the deviation in gain for pixel (x, y). Gain FPN can be represented as the pixel to pixel variation of a(x, y) and its magnitude is  $\sigma_{\Delta h}/h_0$ . Although gain FPN can slowly vary with temperature and aging, we assume here that a(x, y) is constant while capturing several frames with the imager. Note that a(x, y) = 1 for all (x, y) in an ideal sensor having no gain FPN.

To quantify the effect of different device parameters on the gain FPN, we define parameter values  $Z_1, Z_2, ..., Z_k$  and express  $Z_i = z_i + \Delta Z_i$  where  $z_i$  the nominal value of the device parameter and  $\Delta Z_i$  is the variation of  $Z_i$ . Thus the variation of gain  $\Delta H$  can be represented as

$$\Delta H = \sum_{i=1}^{k} \frac{\partial h}{\partial z_i} \cdot \Delta Z_i.$$

(3.2)

For Passive Pixel Sensor (PPS),  $Z_i$ s are photodiode area  $A_D$  and the feedback capacitance  $C_f$  in the column opamp. For Active Pixel Sensor (APS),  $Z_i$ s are  $A_D$ , photodiode capacitance  $C_D$ , the gain of the source followers  $A_{sf}$  and the gain of ADC  $A_{ADC}$  (if there are more than 1 ADC). For Digital Pixel Sensor (DPS),  $Z_i$ s are  $A_D$ ,  $C_D$  and  $A_{ADC}$ .

Some device parameters contribute to individual pixel gain non-uniformity whereas some others contribute to row or column gain non-uniformity. Row or column component appears as stripes in the image and can result in significant image quality degradation. Thus, we can divide  $\Delta H$  in Equation 3.2 into pixel gain FPN component  $\Delta H_X$ , column gain FPN component  $\Delta H_Y$  and row gain FPN component  $\Delta H_Z$ . This model will later be used in Section 3.4 to synthetically generate video sequence corrupted by gain FPN.

We assume brightness constancy, which implies that brightness is constant along each motion trajectory. Brightness constancy is commonly assumed in the development of many video processing and computer vision algorithms [50, 48]. Thus, if F+1 frames are captured using an  $M \times N$  pixel image sensor, the ideal pixel intensity value at t,  $i_0(x, y, t)$ , can be expressed in terms of the ideal pixel intensity at t = 0,

$$j(x,y) = i_0(x,y,0)$$

, as

$i_0(x+d_x(x,y,t),y+d_y(x,y,t),t) = j(x,y)$ , for  $x = 1, \dots, M$ ,  $y = 1, \dots, N$ , and  $t = 0, \dots, F$ .

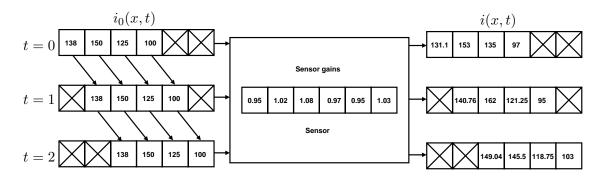

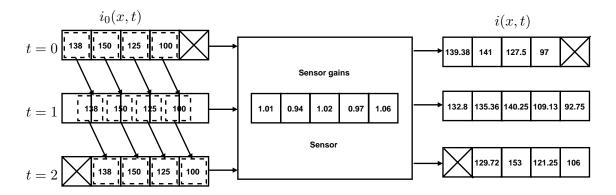

(3.3)